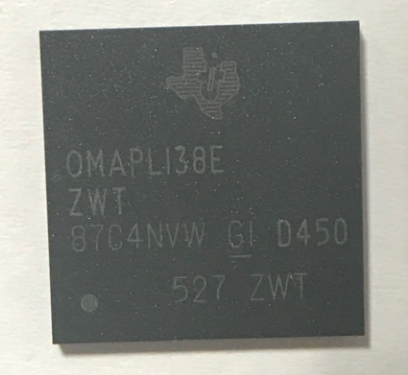

OMAPL138EZWTD4

- 制造商编号:

- OMAPL138EZWTD4

- 品牌:

- TI

- 库存数量:

- 40件

- 售价:

- ¥128.000

- 上架时间:

- 2019/4/23 19:44:24

| 数量 | 价格 |

| 5+ | ¥128.000 |

| 50+ | ¥125.440 |

| 500+ | ¥125.440 |

| 1000+ | ¥125.440 |

| 3000+ | ¥125.440 |

OMAP-L138 C6000 DSP+ARM 处理器 是一款低功耗 应用 处理器,该处理器基于 ARM926EJ-S 和 C674x DSP 内核。该处理器 与其他 TMS320C6000™ 平台 DSP 相比,功耗要小很多。

凭借这款器件,原始设备制造商 (OEM) 和原始设计制造商 (ODM) 能够充分利用全集成混合处理器解决方案的灵活性,迅速将兼具稳健操作系统、丰富用户接口和高处理器性能的器件推向市场。

此器件采用双内核架构(包括一个高性能的 TMS320C674x DSP 内核和一个 ARM926EJ-S 内核),实现了 DSP 与精简指令集计算机 (RISC) 技术二者优势的完美融合。

ARM926EJ-S 是一款 32 位 RISC 处理器内核,可执行 32 位或 16 位指令和处理 32 位、16 位或 8 位数据。该内核采用流水线结构,因此处理器和存储器系统的所有部件能够连续运行。

ARM9 内核配有协处理器 15 (CP15)、保护模块以及具有页表缓冲区的数据和程序存储器管理单元 (MMU)。ARM9 内核配有独立的 16KB 指令缓存和 16KB 数据缓存。这两个缓存均与虚拟索引虚拟标签 (VIVT) 4 路相连。ARM9 内核还配有 8KB 的 RAM(向量表)和 64KB 的 ROM。

该器件的 DSP 内核采用基于 2 级缓存的架构。第 1 级程序缓存 (L1P) 是一个 32KB 的直接映射缓存,第 1 级数据缓存 (L1D) 是一个 32KB 的 2 路组相连缓存。第 2 级程序缓存 (L2P) 包含 256KB 的存储空间,由程序空间和数据空间共享。L2 存储器可配置为映射存储器、缓存或二者的组合。尽管 ARM9 和系统内的其他主机均可访问 DSP L2,但还是额外提供了一个 128KB 的 RAM 共享存储器给其他主机使用,从而避免对 DSP 性能产生影响。

对于支持安全功能的器件,TI 的基本安全启动可为用户保护自主知识产权并防止外部实体修改用户开发的算法。该安全启动流程从一个基于硬件的“信任根”开始,确保代码从一个已知安全的位置开始执行。默认情况下会锁定 JTAG 端口以防止仿真和调试攻击;不过,在应用开发期间的安全启动过程中可以使能 JTAG 端口。启动模块存储在外部非易失性存储器(例如,闪存或 EEPROM)中时处于加密状态,在安全启动期间被装载时会进行解密和验证。加密和解密程序会保护用户 IP,使用户能够安全地设置系统并使器件采用已知可信任的代码开始运行。

基本安全启动使用 SHA-1 或 SHA-256 以及 AES-128 来验证启动映像。另外,基本安全启动使用 AES-128 进行启动映像加密。安全启动流程采用多层加密机制,不但可以保护启动过程,而且能够安全地升级启动和应用软件代码。该器件使用 1 个 128 位的器件专用密钥来保护用户密钥,该 128 位密钥由经过 NIST-800-22 认证的随机数发生器生成,并且仅对该器件是已知的。当需要更新时,客户可使用密钥创建一个新的加密映像。之后,器件可通过外部接口(例如,以太网)来获取该映像并覆盖现有代码。有关支持的安全 特性 或 TI 基本安全启动的更多详细信息,请参见《TMS320C674x/OMAP-L1x 理器安全用户指南》。

外设集包括:1 个具有管理数据输入/输出模块 (MDIO) 的 10Mbps/100Mbps 以太网介质访问控制器 (EMAC);1 个 USB2.0 OTG 接口;1 个 USB1.1 OHCI 接口;2 个 I2C 总线接口;1 个具有 16 个串行器和 FIFO 缓冲器的多通道音频串行端口 (McASP);2 个具有 FIFO 缓冲器的多通道缓冲串行端口 (McBSP);2 个支持多片选的串行外设接口 (SPI);1 个可配置的 16 位主机端口接口 (HPI);多达 9 组通用输入/输出 (GPIO) 引脚(每组包含 16 个引脚,每个引脚均支持可编程的中断和事件生成模式,并且支持与其他外设复用);3 个 UART 接口(均支持 RTS 和 CTS);2 个增强型高分辨率脉宽调制器 (eHRPWM) 外设;3 个 32 位增强型捕捉 (eCAP) 模块外设(可配置为 3 个捕捉输入或 3 个 APWM 输出);2 个外部存储器接口(一个是用于慢速存储器或外设的异步 SDRAM 外部存储器接口 (EMIFA),另一个是高速 DDR2/移动 DDR 控制器)。

EMAC 为器件和网络之间提供了一个高效接口。无论是在半双工模式还是全双工模式下,EMAC 都支持 10Base-T 和 100Base-TX 或者 10Mbps 和 100Mbps。此外,该器件还提供了一个针对 PHY 配置的 MDIO 接口。EMAC 支持 MII 和 RMII 接口。

串行 ATA (SATA) 控制器提供了一个连接至海量数据存储器件的高速接口。SATA 控制器支持 SATA I (1.5Gbps) 和 SATA II (3.0Gbps)。

通用并行端口 (uPP) 提供了一个连接至多种类型的数据转换器、FPGA 或其他并行器件的高速接口。uPP 的两个通道均支持可编程的数据宽度,可编程范围为 8 位至 16 位。另外,还支持单倍数据速率或双倍数据速率传输以及 START、ENABLE 和 WAIT 信号,用以控制各类数据转换器。

视频端口接口 (VPIF) 提供了灵活的视频 I/O 端口。

丰富的外设集提供了控制外设以及与外部处理器进行通信的功能。如需了解每个外设的详细信息,请参见本文档中的有关章节以及相关外设参考指南。

该器件配有一套完整的 ARM9 和 DSP 开发工具。这套工具包括 C 语言编译器,用于简化编程和调度过程的 DSP 汇编优化器以及用于查看源代码执行的 Windows®调试器接口。

特性

双核 SoC

375MHz 和 456MHz ARM926EJ-S™精简指令集 (RISC) MPU

375MHz 和 456MHz C674x 定点和浮点超长指令字 (VLIW) 数字信号处理器 (DSP)

ARM926EJ-S 内核

32 位和 16 位 (Thumb®) 指令

DSP 指令扩展

单周期 MAC

ARM Jazelle®技术

嵌入式 ICE-RT™,用于实时调试

ARM9™存储器架构

16KB 的指令缓存

16KB 的数据缓存

8KB 的 RAM(向量表)

64KB 的 ROM

C674x 指令集 特性

C67x+ 和 C64x+ ISA 的超集

高达 3648 MIPS 和 2746 MFLOPS

可按字节寻址(8 位、16 位、32 位和 64 位数据)

8 位溢出保护

位域提取、设定、清空

正常化、饱和、位计数

紧凑 16 位指令

C674x 二级缓存架构

32KB 的 L1P 程序 RAM/缓存

32KB 的 L1D 数据 RAM/缓存

256KB 的 L2 统一映射 RAM/缓存

灵活 RAM/缓存分区(L1 和 L2)

增强型直接存储器访问控制器 3 (EDMA3):

2 个通道控制器

3 个传输控制器

64 个独立 DMA 通道

16 个快速 DMA 通道

可编程传输突发尺寸

TMS320C674x 浮点 VLIW DSP 内核

混合精度 IEEE 浮点乘法支持高达:

定点乘法每个时钟周期支持 2 次 32 × 32 位乘法、4 次 16 × 16 位乘法或 8 次 8 × 8 位乘法,而且还支持复杂的乘法

每时钟 2 次 SP × SP → SP 运算

每 2 个时钟 2 次 SP × SP → DP 运算

每 3 个时钟 2 次 SP × DP → DP 运算

每 4 个时钟 2 次 DP × DP → DP 运算

支持 32 位整型,SP(IEEE 单精度/32 位)和 DP(IEEE 双精度/64 位)浮点数

每个时钟支持多达 4 次 SP 加法,每 2 个时钟支持多达 4 次 DP 加法

每个周期支持多达 2 次浮点数(SP 或 DP)倒数逼近 (RCPxP) 和平方根倒数逼近 (RSQRxP) 运算

具备非对齐支持的 Load-Store 架构

64 个通用寄存器(32 位)

6 个 ALU(32 位和 40 位)功能单元

2 个乘法功能单元:

指令压缩减少代码尺寸

所有指令所需条件

取模循环运算的硬件支持

受保护模式运行

对于错误检测和程序重定向的额外支持

软件支持

TI DSPBIOS™

芯片支持库和 DSP 库

128KB 的 RAM 共享存储器

1.8V 或 3.3V LVCMOS I/O(USB 和 DDR2 接口除外)

2 个外部存储器接口:

具有 256MB 地址空间的 16 位 DDR2 SDRAM

具有 256MB 地址空间的 16 位 mDDR SDRAM

NOR(8 位宽或 16 位宽数据)

NAND(8 位宽或 16 位宽数据)

具有 128MB 地址空间的 16 位 SDRAM

EMIFA

DDR2/移动 DDR 存储器控制器,有以下两种选项:

3 个可配置的 16550 型 UART 模块:

含调制解调器控制信号

16 字节 FIFO

16x 或 13x 过采样选项

LCD 控制器

2 个串行外设接口 (SPI),每个接口都有多个芯片选择

2 个多媒体卡 (MMC)/安全数字 (SD) 卡接口,具有安全数据 I/O (SDIO) 接口

2 个主/从内部集成电路

(I2C Bus™)1 个主机端口接口 (HPI),通过 16 位宽的多路复用地址和数据总线实现高带宽

可编程实时单元子系统 (PRUSS)

时钟选通

在一个单一 PSC 时钟选通域下的完整子系统

32 位 Load-Store 精简指令集计算机 (RISC) 架构

每个内核 4KB 的指令 RAM

每个内核 512 字节的数据 RAM

可通过软件禁用 PRUSS 以实现节能

除了 PRU 内核的正常 R31 输出,还会从子系统中导出每个 PRU 的寄存器 30。

2 个独立的可编程实时单元 (PRU) 内核

标准的电源管理机制

专用中断控制器

专用开关中心源

具有集成型 PHY (USB1) 的 USB 1.1 OHCI (主机)

具有集成型 PHY 的 USB 2.0 OTG 端口 (USB0)

USB 2.0 高速和全速客户端

USB 2.0 高速、全速和低速主机

端点 0(控制)

端点 1、2、3 和 4(控制、批量、中断或 ISOC)RX 和 TX

1 个多通道音频串行端口 (McASP):

2 个时钟域和 16 个串行数据引脚

支持时分复用 (TDM),I2S,和相似格式

支持动态互联网技术 (DIT)

用于发送和接收的 FIFO 缓冲器

2 个多通道缓冲串行端口 (McBSP):

支持 TDM,I2S,和相似格式

AC97 音频编解码器接口

电信接口(ST 总线,H100)

128 通道时分复用 (TDM)

用于发送和接收的 FIFO 缓冲器

10/100Mbps 以太网 MAC (EMAC):

符合 IEEE 802.3 标准

MII 介质独立接口

RMII 简化的介质独立接口

管理数据 I/O (MDIO) 模块

视频端口接口 (VPIF):

2 个 8 位 SD (BT.656)、单个 16 位或单个原始(8 位、10 位和 12 位)视频捕捉通道

2 个 8 位 SD (BT.656)、单个 16 位视频显示通道

通用并行端口 (uPP):

到现场可编门阵列 (FPGA) 和数据转换器的高速并行接口

两个通道的数据宽度为 8 位至 16 位(包括 8 位和 16 位)

单倍数据速率或双倍数据速率传输

支持具有 START、ENABLE 和 WAIT(开始、使能和等待)控制的多个接口

串行高级技术附件 (SATA) 控制器:

支持 SATA I (1.5Gbps) 和 SATA II

(3.0Gbps)支持全部 SATA 电源管理 特性

高达 32 条的硬件辅助本地命令队列 (NCQ)

支持端口复用器和基于命令的开关

具有 32kHz 振荡器和独立电源轨的实时时钟 (RTC)

3 个 64 位通用定时器(每一个可配置为 2 个 32 位定时器)

1 个 64 位通用定时器或看门狗定时器(可配置为 2 个 32 位定时器)

2 个增强的高分辨率脉宽调制器 (eHRPWM):

具有周期和频率控制的专用 16 位时基计数器

6 个单边沿输出、6 个双边沿对称输出或 3 个双边沿非对称输出

死区生成

高频载波实现的脉宽调制 (PWM) 斩波

触发区输入

3 个 32 位增强型捕捉 (eCAP) 模块:

可配置为 3 个捕捉输入或 3 个辅助脉宽调制器 (APWM) 输出

多达 4 个事件时间戳的单脉冲捕捉

封装:

361 焊球无铅塑封球栅阵列 (PBGA) [ZCE 后缀]、0.65mm 焊球间距

361 焊球无铅 PBGA [ZWT 后缀]、

0.80mm 焊球间距商业级、扩展级或工业级温度